# Chapitre 4 : Interfaçage du microprocesseur 8086

Un système à microprocesseur très simple est composé des parties suivantes:

- (1) Microprocesseur 8086 (Minimum Mode)

- (2) Générateur d'horloge 8284A (15 MHz Crystal)

- (3) Bus système (Demultiplexed and Buffered)

- (4) Mémoire système (ROM & RAM)

- (5) I/O système (Switches and LEDs)

## IV.1 Microprocesseur 8086 (Minimum Mode)

Le 8086 a Deux modes de fonctionnement :

**Mode minimum (MN/MX = 1):** Ce mode permet de diminuer le nombre de circuits extérieurs pour les systèmes à processeur unique. Le processeur prend en charge la gestion des bus.

**Mode maximum (MN/MX = 0) :** ces signaux de commande sont produits par un contrôleur de bus, le 8288. Ce mode permet de réaliser des systèmes multiprocesseurs.

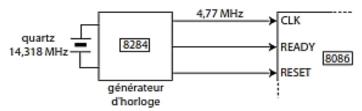

## IV.2 Générateur d'horloge

Le 8284A est un circuit intégré conçu spécialement pour les microprocesseurs 8086/8088. Ce circuit fournit les fonctions ou les signaux de bases suivantes: génération d'horloge, RESET, READY.

Figure IV.1: Interfaçage du 8284 avec le 8086

# IV.3 Bus système (Demultiplexed and Buffered)

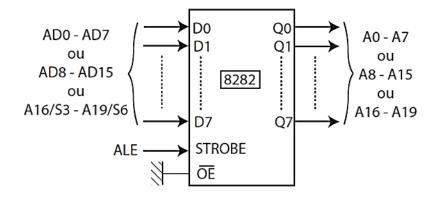

Avant d'utiliser le microprocesseur 8086 avec les mémoires ou les interfaces E /S, les pines multiplexé (adresse /données et d'adresses/lignes d'état) doivent être démultiplexes. Il faut aussi amplifier le courant fourni par ces lignes pour pouvoir commander d'autres composants dans le système.

Le démultiplexage des signaux AD0 à AD15 (ouA16/S3 à A19/S6) sefait à l'aide d'un verrou (latch), ensemble de bascules D. cet événement est indiqué par le signal ALE.

Circuit de demultiplexage A/D:

Exemples de bascules D: circuits 8282, 74373, 74573.

Figure IV.2: bascules D circuits 8282

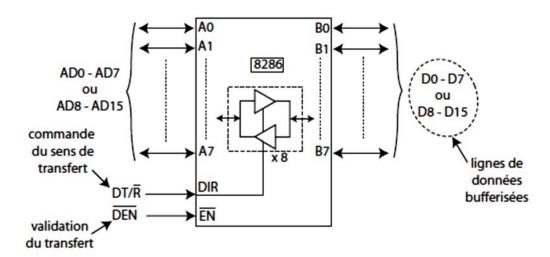

Si plus de 10 composants sont attachés aux broches de bus, l'ensemble du système 8086 doit être amplifié. Les broches démultiplexés (adresse bus A19-A0 et BHE) sont déjà amplifiées par les verrous (latch). Donc, il faut amplifier le bus de données D15 - D0. Le bus de données est bidirectionnel, nous devons utiliser des tampons (buffers) bidirectionnels :

Exemples de tampons de bus : circuits transmetteurs bidirectionnels 8286 ou 74245 :

Figure IV.3: circuits transmetteurs bidirectionnels 8286

**Remarque :** Les signaux de bus de contrôle (M/IO, RD et WR) les signaux de bus de contrôle sont des signaux unidirectionnels. Par conséquent, nous avons besoin d'utiliser des tampons unidirectionnels tels que le buffer 74LS244.

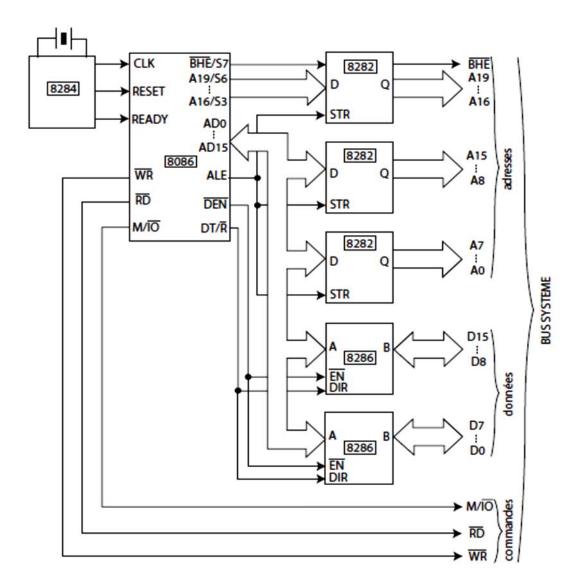

La figure suivante montre la conception de bus système de µp 8086

Figure IV.4 : conception de bus système de µp 8086

# IV.4 Mémoire système (ROM & RAM)

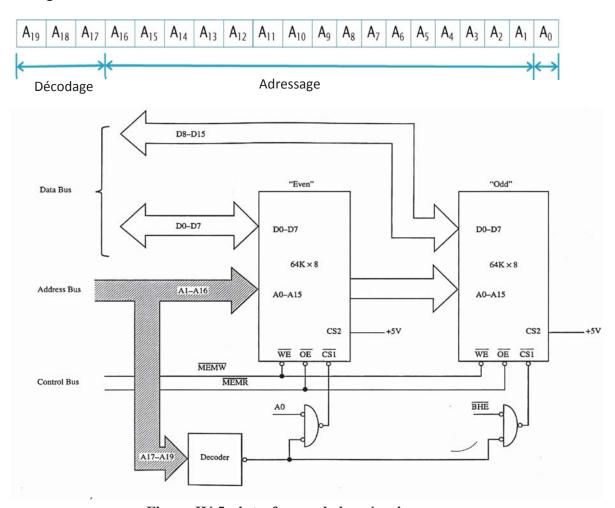

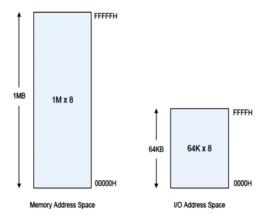

Le microprocesseur 8086 à 20 bits d'adresses (A19 - A0) donc un espace mémoire D'une capacité de 1 Mo.

Par conséquent, le micro-processeur 8086 nécessite que cet espace mémoire soit organisé en deux banques (512 Ko chacune) appelées les banques paires et impaires.

La partie paire est connectée au bus de données D0/D7, et la partie impaire est connectée au bus D8/D15. Ces deux banques sont sélectionnées par A0 est BHE.

Puisque le 8086 a un espace mémoire D'une capacité de 1 Mo. D'où la possibilité d'avoir jusqu'à 8 blocs mémoire de 128Ko chacun.

Si on va utiliser deux boitiers mémoire RAM de 64 ko chacun. Donc on a 16 lignes d'adresse ( $64K = 2^6 \times 2^{10} = 2^{16}$ ).

Le 8086 sera interfacé à la RAM comme suit:

Les lignes d'adresse les moins significatives A16-A1 sont utilisées pour adresser des emplacements de mémoire dans la RAM.

Les lignes d'adresse les plus significatives A19-A17 sont utilisées pour sélectionner la plage d'adresses nécessaires dans l'espace de mémoire de 8086 (sélectionner les deux boitiers RAM), comme sur figure.

Figure IV.5 : interfaçage de la mémoire.

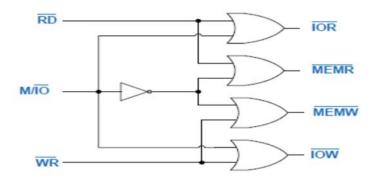

**Remarque :** Le microprocesseur 8086 fournit trois signaux de commande RD, WR et M / IO qui peuvent être décodés comme représentés sur la figure suivante : les signaux (MEMR, MEMW, IOR et IOW).

Figure IV.6 : décodage signaux lecture et écriture mémoire et I/O.

### IV.5 E/S système (Switches and LEDs)

Les ports d'E/S sont utilisés pour l'échange de données entre le µp et un périphérique. Un port d'E/S est similaire à un emplacement mémoire sauf que chaque port doit avoir sa propre adresse.

Avec les processeurs 80x86, on a 16 lignes d'adresse pour le port d'E/S avec une taille 64Ko. Il existe deux méthodes différentes d'interface d'E/S à microprocesseur 8086:

E/S isolé (adresse cartographique);

E / S Mappé en mémoire (adresse cartographique).

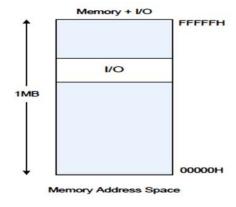

### IV.5.1 Adresse cartographique

Les adresses des ports d'E/S appartiennent au même espace mémoire que les circuits mémoires (Les adresses des ports d'E/S appartiennent au même espace mémoire que les circuits mémoires (on dit que les E/S sont mappées en mémoire)

#### IV.5.2 Adressage indépendant

Le microprocesseur considère deux espaces distincts :

- L'espace d'adressage des mémoires

- L'espace d'adressage des ports d'E/S

Tableau IV.1: Comparaison entre Adressage cartographique et indépendant

| Adresse cartographique                              | Adressage indépendant                          |

|-----------------------------------------------------|------------------------------------------------|

| • l'espace d'adressage des mémoires diminue         | • contrairement à l'adressage                  |

| • l'adressage des ports d'E/S se fait avec une      | cartographique, l'espace mémoire total         |

| adresse de même longueur que pour les cases         | adressable n'est pas diminué                   |

| mémoires                                            | • l'adressage des ports d'E/S peut se faire    |

| • toutes les instructions employées avec des cases  | avec une adresse plus courte que les circuits  |

| mémoires peuvent être appliquées aux ports          | mémoires                                       |

| d'E/S.                                              | • les instructions utilisées pour l'accès à la |

| • Les mêmes instructions permettent de lire et      | mémoire ne sont plus utilisables pour          |

| écrire dans la mémoire et les ports d'E/S, tous les | l'accès aux ports d'E/S, ceux-ci disposent     |

| modes d'adressages étant valables pour les E/S      | d'instructions spécifiques                     |

**Remarque :** la mémoire et les ports I/O partage le même bus de données et d'adresse, c'est Le signal M/IO qui permet de différencier l'adressage de la mémoire de l'adressage des ports E/S :

- pour un accès à la mémoire,  $M/\overline{IO} = 1$ ;

- pour un accès aux ports d'E/S,  $M/\overline{IO} = 0$ .

Les instructions utilisées pour R/W d'un port sont « IN / OUT ». Il existe deux types d'accès, accès direct et un autre indirect. Les registres utilisés sont l'accumulateur « AL / AX » et le registre de données « DX ». Les instructions directes d'E / S fournissent l'adresse de port (qui doit être un nombre compris entre 0 et FFh).

Si l'adresse du port d'E/S est sur un octet:

| Lecture d'un port d'E/S                 | Ecriture d'un port d'E/S                  |

|-----------------------------------------|-------------------------------------------|

| IN AL, @: lecture d'un port sur 8 bits  | OUT @, AL: écriture d'un port sur 8 bits  |

| IN AX, @: lecture d'un port sur 16 bits | OUT @, AX: écriture d'un port sur 16 bits |

Pour accéder à la plage complète des ports d'E/S de 0000H à FFFFH, les instructions indirectes d'E / S doivent être utilisées.

Pour ces instructions, le registre DX doit être préchargé avec l'adresse du port.

• si l'adresse du port d'E/S est sur deux octets:

| Lecture d'un port d'E/S                  | Ecriture d'un port d'E/S                   |

|------------------------------------------|--------------------------------------------|

| IN AL, DX : lecture d'un port sur 8 bits | OUT DX, AL : écriture d'un port sur 8 bits |

| IN AX, DX: lecture d'un port sur 16 bits | OUT DX, AX: écriture d'un port sur16 bits  |

Où le registre DX contient l'adresse du port d'E/S à : lire / écrire.