MKUB, Level: 2LMD Module: Operating Systems 1 Duration: 45 min 04/05/2023

# **Test 2 Solution**

#### Exercise 1 (6 marks=1+1+1+1+2):

1. How many page frames are in physical memory?

Number of page frames = Physical mem size/frame size= 2\*2<sup>30</sup>/ 2<sup>6</sup>\* 2<sup>10</sup> = 2<sup>15</sup> frame

2. What is the bit size of a page table entry?

Size of a PT input = number of bits to encode a frame + 1 presence bit

- = 15 + 1 = 16 bits

- 3. What is the number of entries in the page table?

Number of entries in the PT = Size of the PT / size of an entry in the PT = 128 Ko / 16

- $= 2_7 * 2^{10} * 2_3 / 2_4 = 2^{16}$  entries

- 4. What is the size of the virtual memory of this architecture?

Virtual mem size = number of pages \* size of a page

- = Number of entries in the PT \* size of a page

- $= 2^{16} * 2^{16} = 2_{32}$  octets = 4Go

- 5. Consider the following two logical addresses expressed in decimal: 1024 and 65540.

Give the corresponding physical addresses (expressed in decimal).

logical @= 1024

page size =

$$2^{16} = 65536$$

; page  $n^{\circ} = 0$ ; offset = 1024; frame  $n^{\circ} = 0$

physical @ = 0\*65536 + 1024 = 1024

logical @= 65540; Taille page =  $2^{16}$  = 65536; page n° = 1; offset = 4

For page 1, the presence/absence bit =0, hence the page is not loaded into memory.

We cannot know the physical address.

#### Exercise 2 (6 marks=1+1+1+1+1+1):

1. Perform the access sequence with the replacement strategies FIFO, Optimal, and LRU with a memory capacity of 4 frames, and repeat FIFO with 5 frames. Calculate page fault and page fault rate in each case.

#### 135424321053504354321345

#### a. FIFO (with 4 frames)

| Requests: | 1 | 3 | 5 | 4 | 2 | 4 | 3 | 2 | 1 | 0 | 5 | 3 | 5 | 0 | 4 | 3 | 5 | 4 | 3 | 2 | 1 | 3 | 4 | 5 |

|-----------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Page 1:   | 1 | 1 | 1 | 1 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 5 |

| Page 2:   |   | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 1 | 1 | 1 | 1 | 1 | 1 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 |

| Page 3:   |   |   | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 2 | 2 | 2 | 2 | 2 |

| Page 4:   |   |   |   | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 1 | 1 | 1 | 1 |

page fault = 13, page fault rate= $13\24 = 54\%$

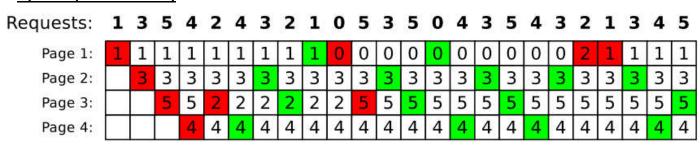

# b. FIFO (with 5 frames)

| Requests: | 1 | 3 | 5 | 4 | 2 | 4 | 3 | 2 | 1 | 0 | 5 | 3 | 5 | 0 | 4 | 3 | 5 | 4 | 3 | 2 | 1 | 3 | 4 | 5 |

|-----------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Page 1:   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Page 2:   |   | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 1 | 1 | 1 | 1 |

| Page 3:   |   |   | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 3 | 3 | 3 |

| Page 4:   |   |   |   | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 5 |

| Page 5:   |   |   |   |   | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 |

page fault = 9, page fault rate= $9\24 = 37\%$

### c. LRU (with 4 frames)

| Requests: | 1 | 3 | 5 | 4 | 2 | 4 | 3 | 2 | 1 | 0 | 5 | 3 | 5 | 0 | 4 | 3 | 5 | 4 | 3 | 2 | 1 | 3 | 4 | 5 |

|-----------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Page 1:   | 1 | 1 | 1 | 1 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 |

| Page 2:   |   | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 1 | 1 | 1 | 1 |

| Page 3:   |   |   | 5 | 5 | 5 | 5 | 5 | 5 | 1 | 1 | 1 | 1 | 1 | 1 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 |

| Page 4:   | 5 |   |   | 4 | 4 | 4 | 4 | 4 | 4 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 2 | 2 | 2 | 2 | 5 |

page fault = 13; page fault rate =  $13 \cdot 24 = 54\%$

## d. Optimal (with 4 frames)

page fault = 9, page fault rate =  $9 \cdot 24 = 37\%$

2. What is the key message of Belady's anomaly?

FIFO result in worse results for certain access sequences with a bigger memory.

3. Why is it impossible to implement the optimal replacement strategy?

Because it is not possible to predict the future and therefore the future request sequence is unknown.